# Prototype design of logic testing controller based on FPGA for interlock system

Presented by Zuchao Zhang<sup>1.3\*</sup>

on behalf of EAST Central Control Team,

B.J.Xiao<sup>1.2.3</sup>, Q.P.Yuan<sup>1.3</sup>, F.Wang<sup>1.3</sup>, Y.Wang<sup>1.3</sup>, R.R.Zhang<sup>1.3</sup>

<sup>1</sup> Institute of Plasma Physics, Hefei Institutes of Physical Science, Chinese Academy of Sciences

<sup>2</sup> University of Science and Technology of China

<sup>3</sup> Institute of Energy, Hefei Comprehensive National Science Center

\*Email: zzc@ipp.ac.cn

- Introduction

- What's in it...

- Logic Rationale

- Hardware Structure

- Software Design

- Program Develop

- Device Assemble

- Controller Testing

- Summary

- Introduction

- What's in it...

- Logic Rationale

- Hardware Structure

- Software Design

- Program Develop

- Device Assemble

- Controller Testing

- Summary

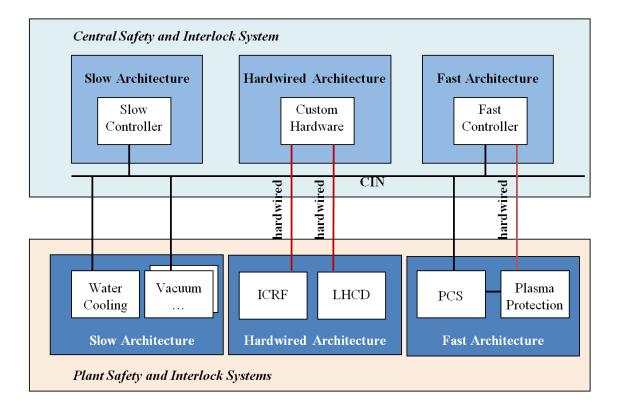

#### **BACKGROUND**

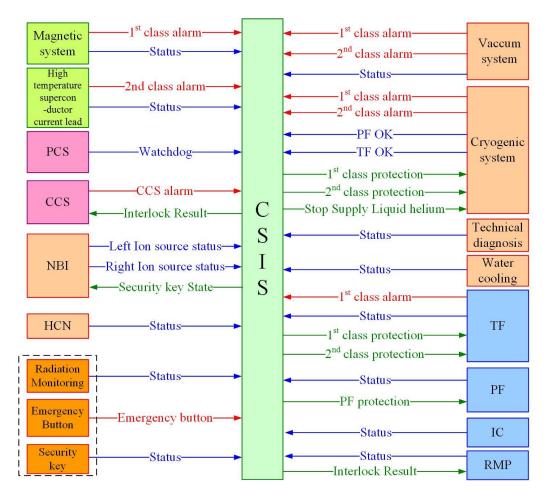

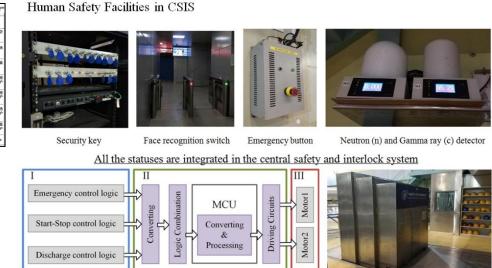

#### EAST Central Safety & Interlock System -- CSIS

• Scans subsystem status, provides protection signal, ensures personal and machine security

during whole experiment.

More stable supervisory and control operation.

#### **BACKGROUND**

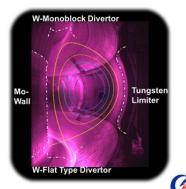

#### new EAST CSIS upgrades with:

- Reviews and upgrades some logical relationship and interface;

- Integrates several new features and plant systems, such as FTD (fishtail divertor), FRS(face recognition signal), etc.;

- Uses SIL-3 safety integrity COTS hardware and configuration software;

- Redundancy mechanism make the system more stable and reliable.

Hardware of new EAST CSIS

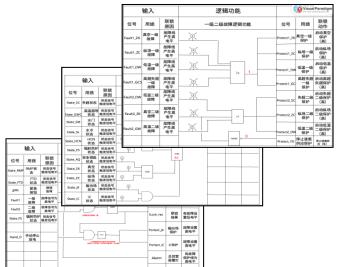

**Main Logic Files for CSIS**

Logic in Part I decides the states of motors' rotation and water door's proper position

**Human Safety Facilities in CSIS**

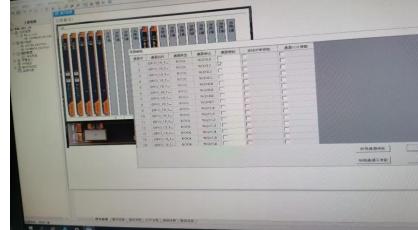

**Configuration Software for CSIS**

#### **Motivation**

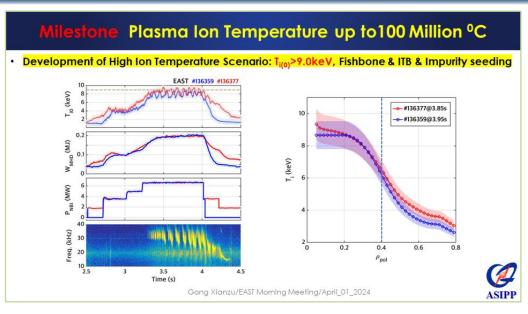

#### **Ongoing EAST Experiments ...**

- from December 2023 to now

- main goals

- G1: Demonstration of long Pulse high performance plasmas with W-Divs in Support of New Baseline for ITER Research Plan

- G2: High Power Operation by ICRH/NBI heating without Li-coating to enhance Ion temperature: PIN~6.0-10MW, Ti0>8.5keV

- more than 14,000 shots (from No.129314)

- 7x24h, no long-term maintenance and repair

No chance to validate and test the new CSIS

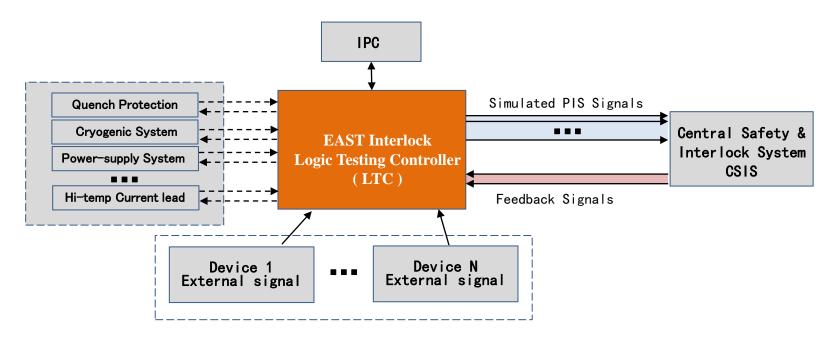

**Logic Testing Controller** (LTC)

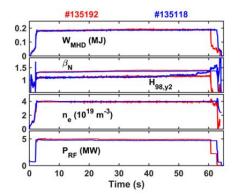

- Stationary 60s high performance plasma with small ELM achieved on tungsten divertor

- / Ip ~ 0.4MA/ne~4.3/H<sub>98y,2</sub>~1.1 ,  $P_{EC}$ =2.7 MW,  $P_{LH}$ =2.2MW

Gong Xianzu/EAST Morning Meeting/March\_18\_2024

#### **Motivation**

- ☐ A plant interlock system simulator, which one or several PIS could be simulated;

- ☐ A mini-CSIS, assists in verifying subsystem interlock functionality;

- ☐ A tool kit, tests the new changes to the software and functions before released when they are considered stable.

Interface functions among LTC and other systems

- Introduction

- What's in it...

- Logic Rationale

- Hardware Structure

- Software Design

- Program Develop

- Device Assemble

- Controller Testing

- Summary

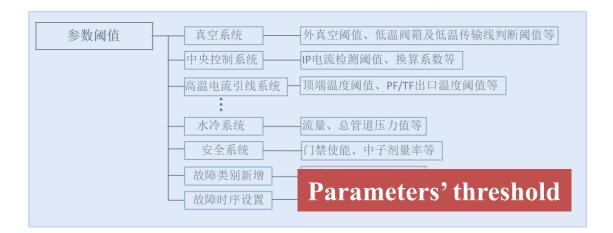

# **Logic Rationale**

#### **Interlock logic information:**

- Collects **ALL** interlock details, over 20 EAST plant systems/devices;

- **Correct** threshold value setting for key parameters, ~ 260;

- Signal types: Status/Alarm/Protection;

- Alarm classification, ~2.

| 在 TF 通电点、上面 1、3、4 信号在一个为级种用不允许 TF 通电。在 PF 是<br>上面 1、2、3、4 信号在一个为限等则也不允许 PF 通电。                                       | ta.                         |       |                                  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|----------------------------------|

|                                                                                                                      | Signal                      | Value | Response                         |

| 从总按延嗣的信号有三个(1)企会生等1000电影信入DCS);<br>1. IT 传统证据信号。表示IT 在货油工桶。<br>2. IT 管理证据信号。表示IT 品货油工桶。<br>3. 直空二级预管信号。使到后停止由内低温泵形成。 | Status                      | High  | OK                               |

| 1                                                                                                                    |                             | Low   | alarm                            |

|                                                                                                                      | 1 <sup>st</sup> class alarm | High  | 1st class protection             |

|                                                                                                                      |                             | Low   | OK                               |

|                                                                                                                      | 2 <sup>nd</sup> class alarm | High  | 2 <sup>nd</sup> class protection |

|                                                                                                                      |                             | Low   | OK                               |

|                                                                                                                      | Protection                  | High  | actuator                         |

|                                                                                                                      |                             | Low   | null                             |

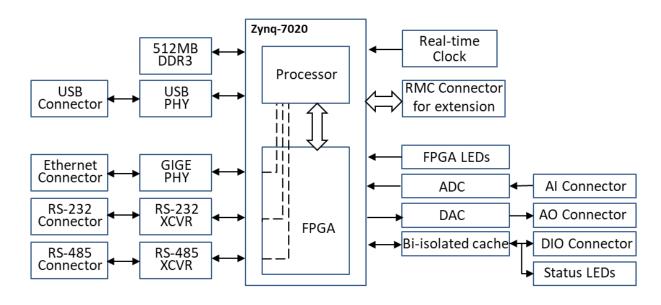

#### **Hardware Structure**

#### **Hardware features:**

- Processor: Xilinx Zynq-7000, XC7Z020 All programmable SoC, ARM Cortex-A9, 512MB, Linux Real-time (32 bit) OS;

- Reconfigurable FPGA: 85,000 logic cells, 106,400 flip-flops,

560 KB available block RAM;

- Connectors: Ethernet Port, RS-232 Serial Port, RS-485 Serial Port,

16 single-ended AI channels, 4 AO channels, 96 DIO

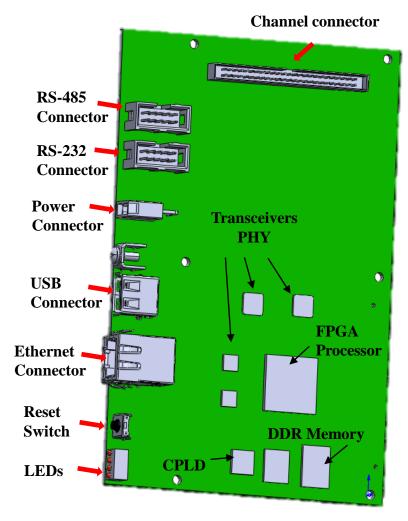

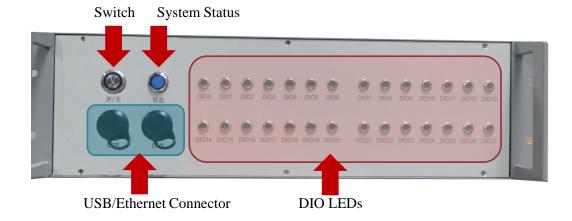

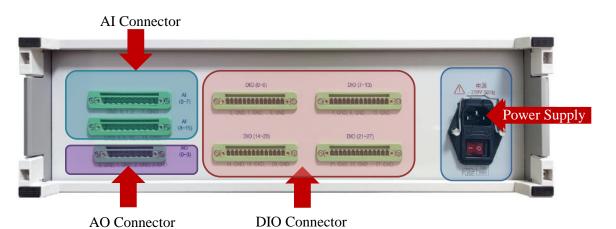

Structure of LTC hardware

LTC Hardware Model

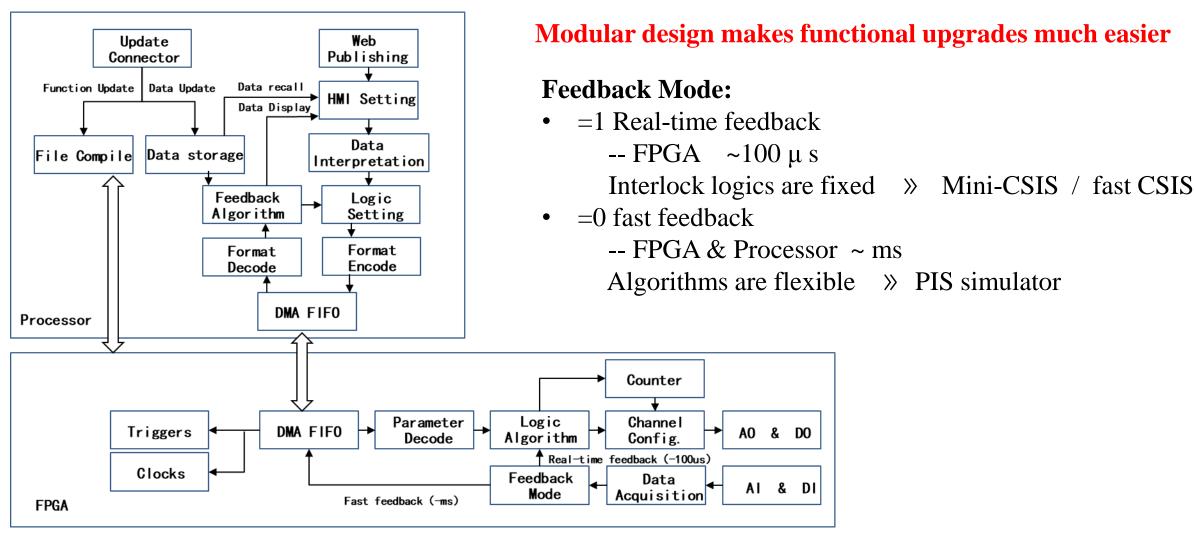

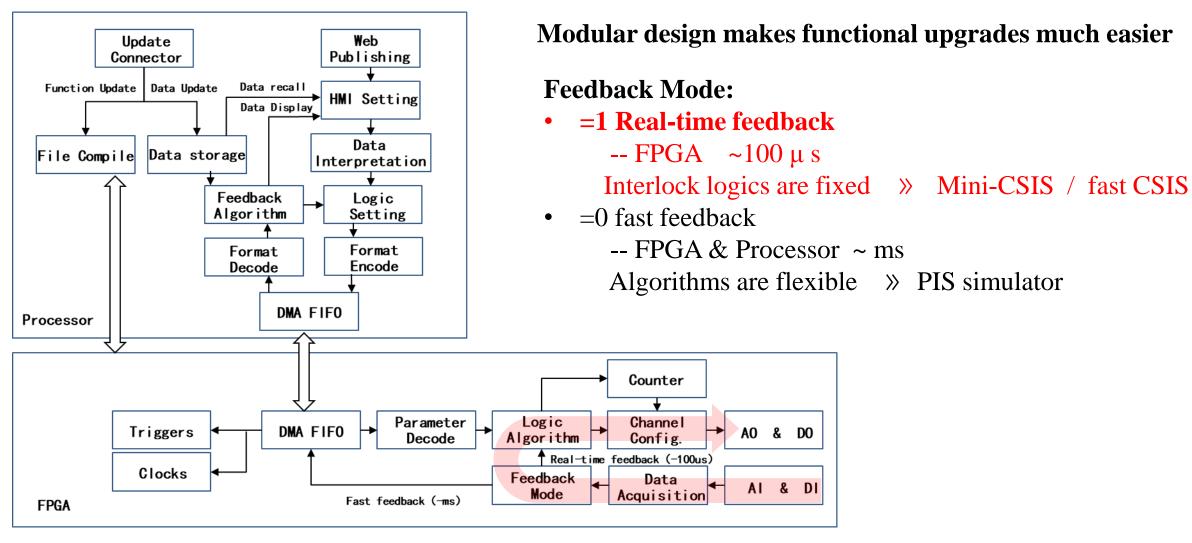

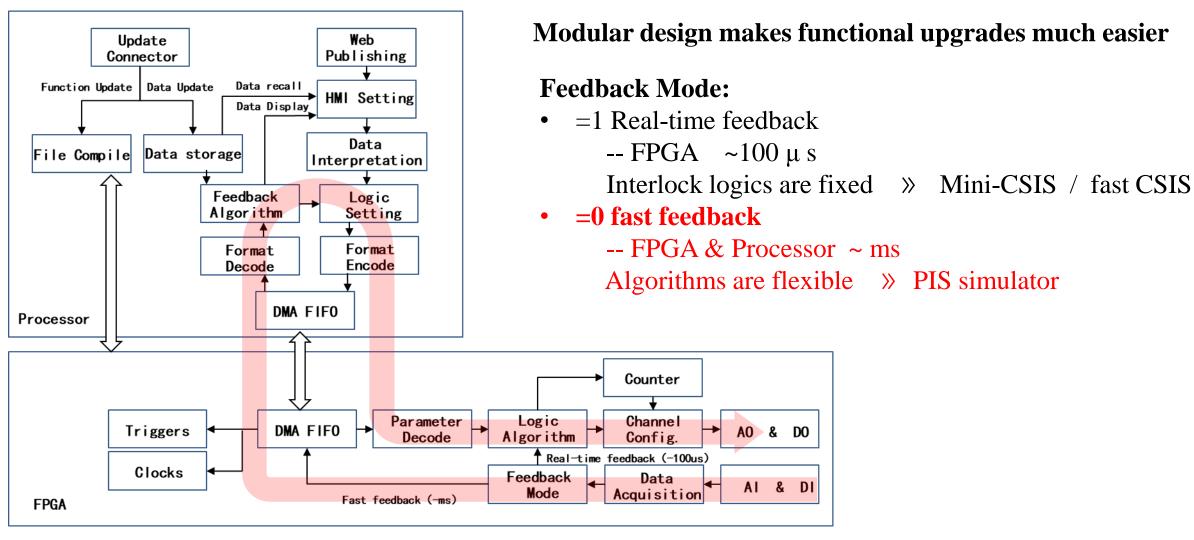

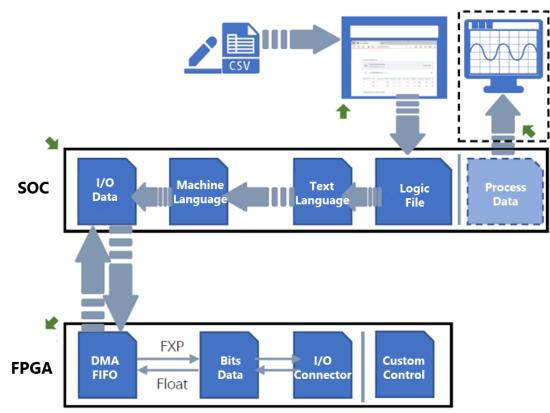

# **Software Design**

**Modular functions for an LTC**

# **Software Design**

Modular functions for an LTC

# **Software Design**

Modular functions for an LTC

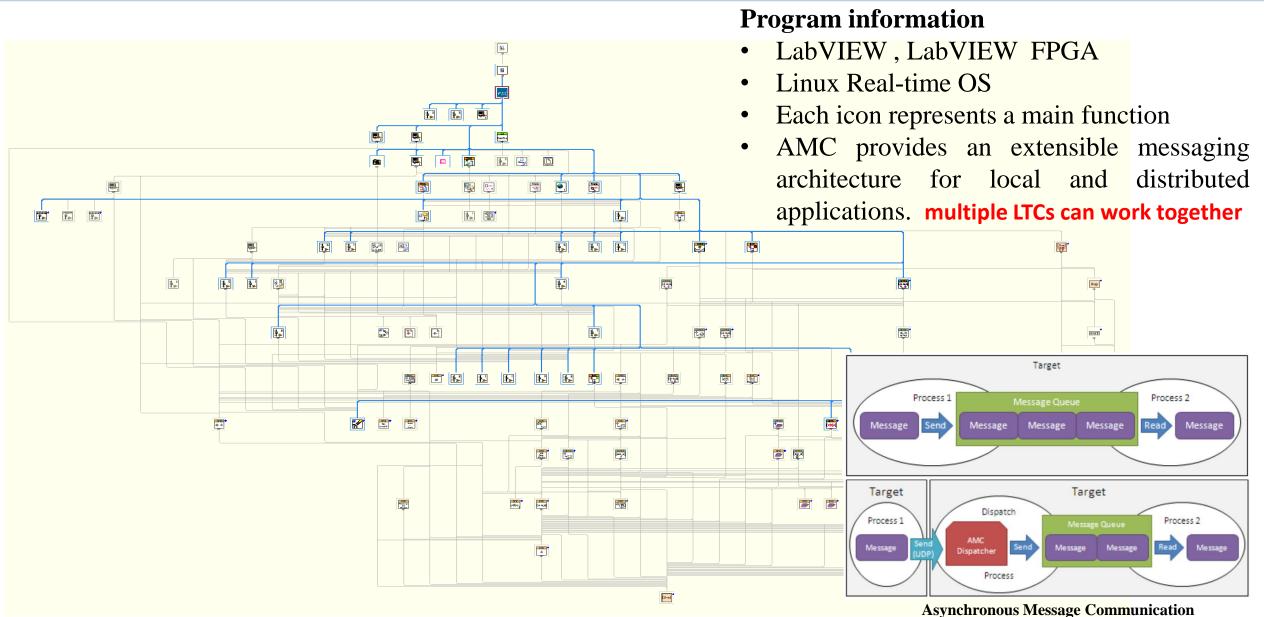

# **Program Develop**

## **Device Assemble**

#### **Font Panel of LTC**

#### **Top View of LTC**

**Rear Panel of LTC**

- Introduction

- What's in it...

- Logic Rationale

- Hardware Structure

- Software Design

- Program Develop

- Device Assemble

- Controller Testing

- Summary

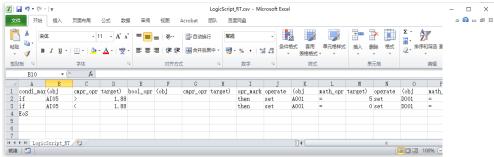

## **Basic functional testing**

• Frequent parameter setting modification, frequent debugging of appropriate thresholds, repeatedly logic test

Logic configuration spreadsheet

Users do not need programming skills, use text language to edit logic in spreadsheet.

Statement such as:

```

if AI5 > 1.88 then set AO1 = 5 set DO0 = 1

if AI5 < 1.88 then set AO1 = 0 set DO0 = 0

```

Users can change the operation logic of signal I/O through text editing without programming, and realize customized logic operation and control output, which can greatly reduce the workload of system debugging and use.

**Data transmission process**

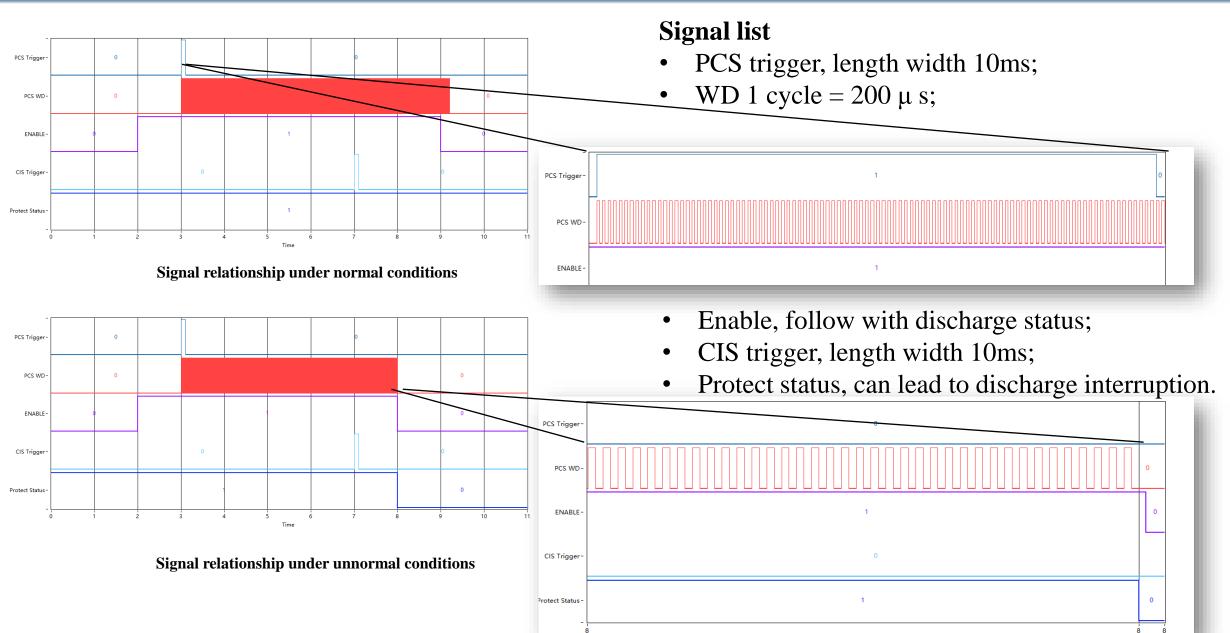

## **PCS** simulator function test - simulation

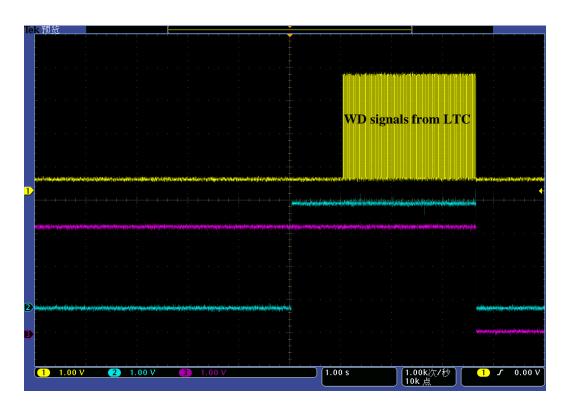

# PCS simulator function test - in reality

**Contents: WD signal terminated prematurely**

Pre-set parameters:

Discharge length: 6 s

PCS trigger time: -1s

PCS work length: 2.6s

Data archived by oscilloscope

- Simulator-PCS WD, WD signal terminated prematurely.

- Simulator- Enable, follow the discharge status.

- mew CSIS Protection, shows abnormal interlock status, lead to discharge interruption.

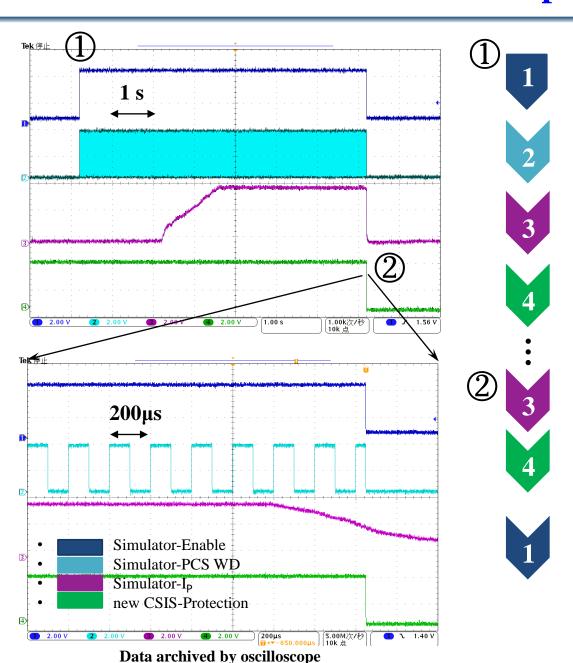

# **New CSIS test-plasma current detection**

LTC generates an enable signal, it represents the length of discharge under normal conditions.

Enable signal activate Simulator-PCS, and output watchdog signal, cycle 200  $\mu$  s.

LTC generates a plasma current signal at preset time (-2s), it simulates the process of plasma discharge.

At the beginning, all the states are normal, and new CSIS-Protection output signal to PIS is high.

Simulator-Plasma current signal value decrease.

New CSIS detects a sharp signal changes, triggers the interlock algorithm, fans out protection signals to PIS

Protection signal turn to 0 means the discharge is terminated, so Simulator-Enable signal end. Waiting ...

On receiving protection signal, PCS stops working, and the WD output is 0.

- Introduction

- What's in it...

- Logic Rationale

- Hardware Structure

- Software Design

- Program Develop

- Device Assemble

- Controller Testing

- Summary

# **Summary**

#### **Logic Testing Controller**

- ☐ LTC has comprehensive EAST PIS interlock logical details, all of subsystems have been involved;

- ☐ LTC is a good tool kit to test the new CSIS before released as PIS simulators;

#### Outlook

- More features will be added, such as touch screen HMI, fiber optic interface, *etc.*;

- □ Optimizing work will be conducted for BEST central interlock system.