## Implementation of an FPGA-based DAQ and Processing system for Neutron-Diagnostics using Nominal Device Support, OpenCL and MTCA

<u>M. Astrain<sup>1</sup></u>, A. Carpeño<sup>1</sup>, S. Esquembri<sup>1</sup>, M. Ruiz<sup>1</sup>, J.Nieto<sup>1</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

Email: miguel.astrain@i2a2.upm.es

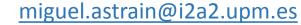

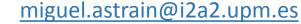

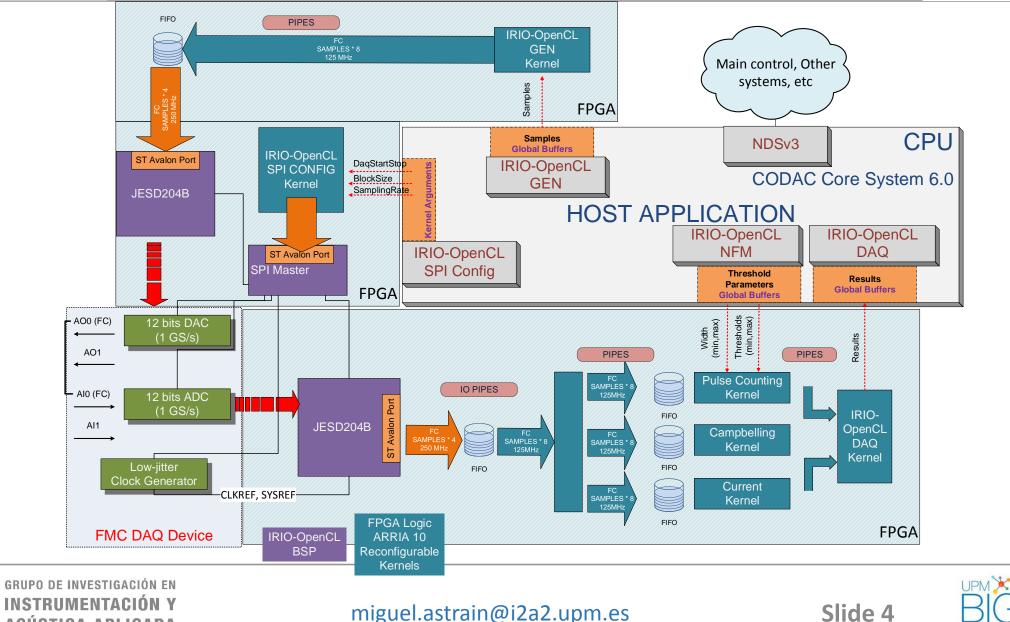

**System Architecture: HW**

- PC + PCIe + MTCA + AMC + (PROCESSING) + (I/O)

- Thursay mini and poster on NDSv3!!

IAEA TM CODAC 2019 May 13 – 17, 2019 | Daejeon

6

ACÚSTICA APLICADA

YE

SCIENCE

- The Intel OpenCL compiler generates an efficient pipeline to process data at very high throughput. HW is described using OpenCL language.

- > FPGA resource utilization with all the IRIO-OpenCL functionality is less than 50%.

- > The hardware is managed using NDSv3 allowing an easy connection to EPICS.

- > The complete platform is integrated in ITER CODAC Core System.

- Today's topic: OpenCL is being extensively used for machine learning applications.

More details in the plenary oral:

**490.** Methodology to standardize the development of FPGA-based intelligent DAQ and processing systems on heterogeneous platforms using OpenCL

## Thursday 9:00

Slide 5

## **Implementation of an FPGA-based DAQ and Processing system for Neutron-Diagnostics** using Nominal Device Support, OpenCL and MTCA an FPGA-based DAQ and Processing system for Neutror

M. Astrain<sup>1</sup>, A. Carpeño<sup>1</sup>, S. Esquembri<sup>1</sup>, M. Ruiz<sup>1</sup>, J.Nieto<sup>1</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

Email: miguel.astrain@i2a2.upm.es

## **Thanks for your attention!!**

This work was supported in part by the Spanish Ministry of Economy and Competitiveness, Projects Nº ENE2015-64914-C3-3-R and Madrid regional government (YEI fund), Grant Nº PEJD-2018-PRE/TIC-8571.

**European Union** Investing in your Future **European Social Fund**

**INSTRUMENTACIÓN Y** ACÚSTICA APLICADA

miguel.astrain@i2a2.upm.es

rator or using the DAC in the FMG ared signal by ADC in FMC module are the EPGA, the algorithm is divided into nplemented using MTCA.4 PCIe pticel link delease to is described in contribution ID 490 NDSv3 ted in part by the Spanish Ministry of Economy and rojects Nº ENE2015-64914-C3-3-R and Madrid st (VEL5und). Grant N8 PEID-2018; PRE/TIC-8521

ostics using NDS, OpenCL and MTCA

International Atomic Energy Agency

Slide 6