Methodology to standardize the development of FPGA-based intelligent DAQ and processing systems on heterogeneous platforms using OpenCL <u>M. Astrain<sup>1</sup></u>, M. Ruiz<sup>1</sup>, S. Esquembri<sup>1</sup>, A. Carpeño<sup>1</sup>, E. Barrera<sup>1</sup>, J. Vega<sup>2</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

<sup>2</sup>Laboratorio Nacional de Fusión, CIEMAT, Madrid, Spain

Email: miguel.astrain@i2a2.upm.es

BACKGROUND

• Design cycles for FPGA based applications are still complex and costly.

•IRIO was developed for the PXI platform, mainly FlexRIO and cRIO.

•Standardization adds value to high-level languages, reducing the development times, by reusing existing code.

•OpenCL opens to new manufacturers and heterogeneous devices.

## **METHODS**

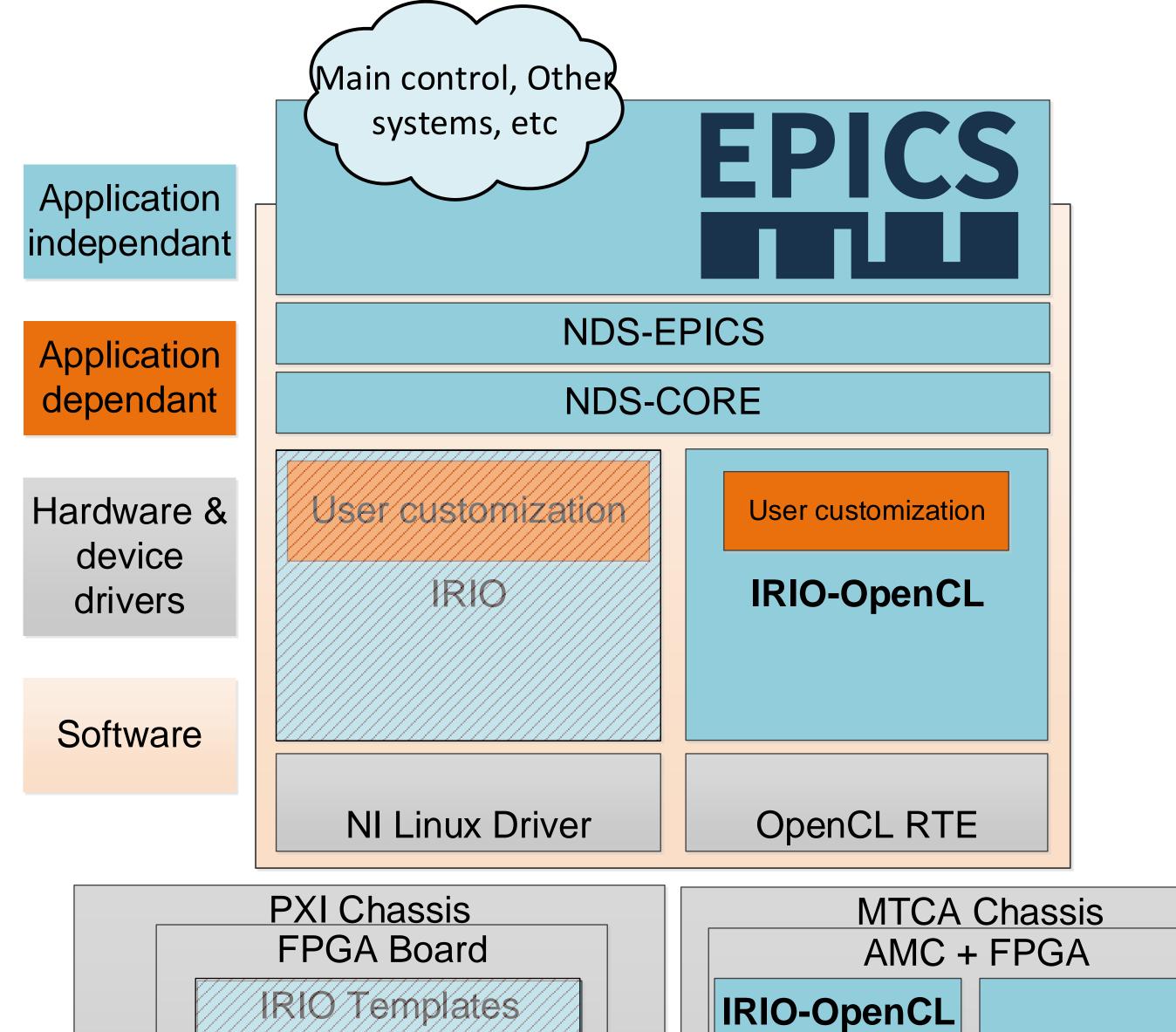

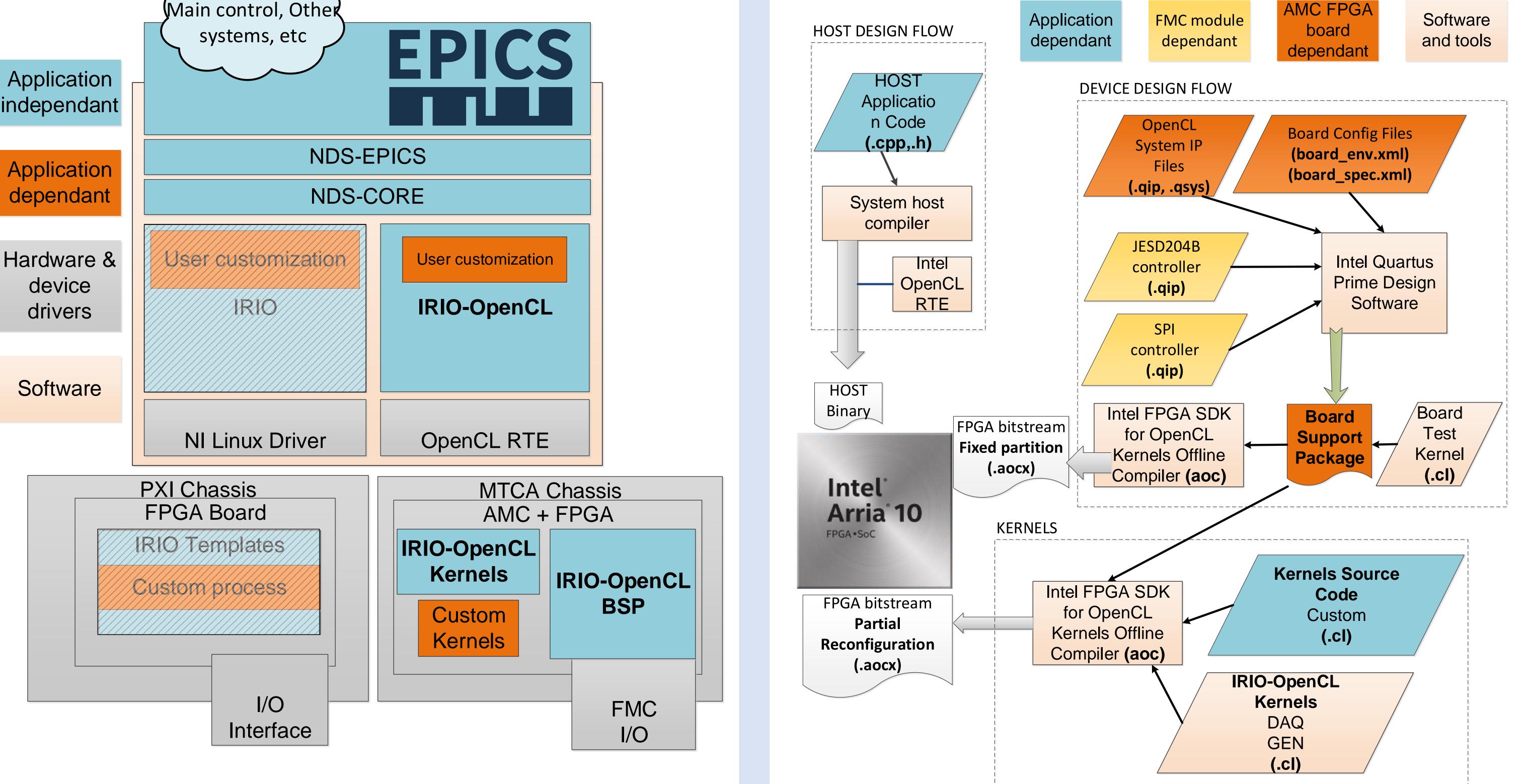

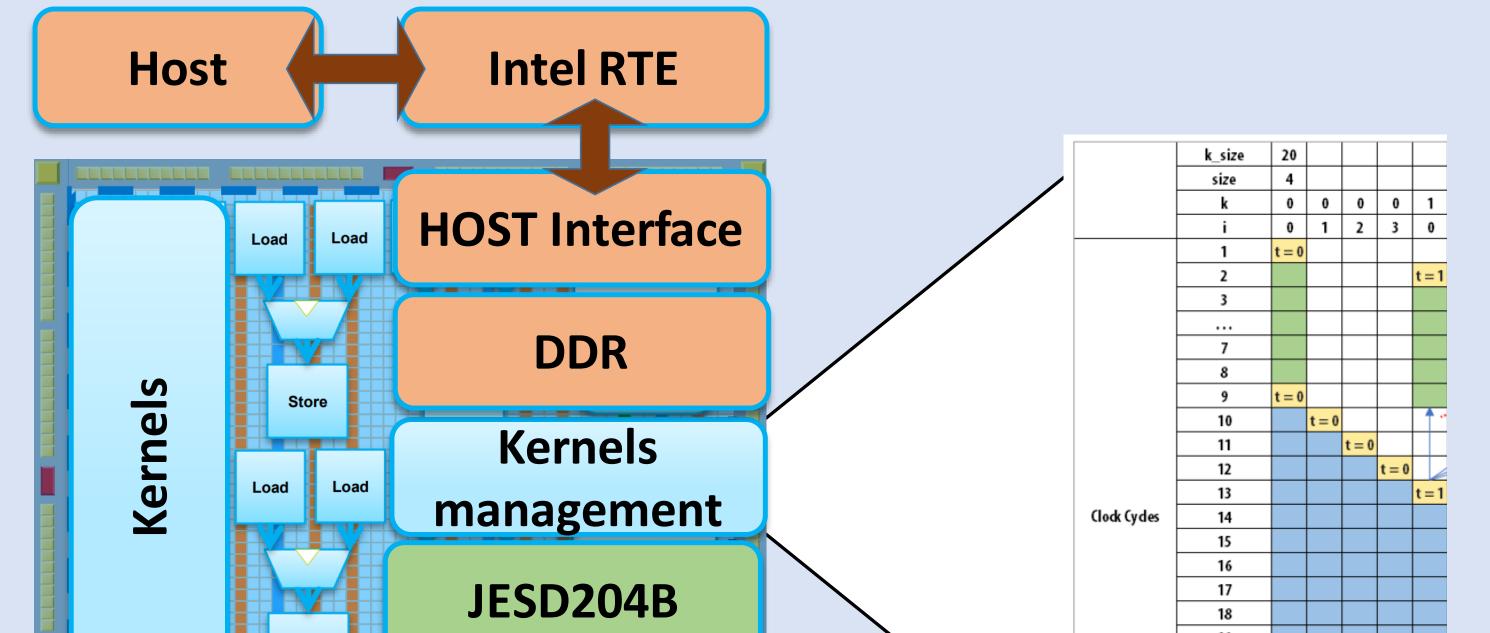

NDSV3 supports hardware functionality on a tree like structure of nodes. By creating IRIO-OpenCL kernels and host code we can recreate this functionality on the FPGA.

**ID: 490**

- Changing processing algorithms is easy. (Blue) 1.

- Changes to I/O hardware requires minor changes. (Yellow)

3. AMC FPGA Board changes require BSP porting. (Orange)

## IMPLEMENTATION

- OpenCL is built as a parallel computing language.

- It uses C/C++ code and a robust memory model.

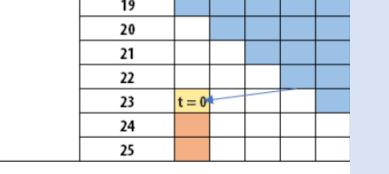

- **Parallelism** on the FPGA is costly on area, it is rather achieved by pipelining the Kernels to generate a very fast stream of data.

- The board support package (**BSP**) contains all the necessary hardware ulletto manage DDR, JESD204B, Host PCIe and memory interface, ... and kernels execution.

## ACKNOWLEDGEMENTS

This work was supported in part by the Spanish Ministry of Economy and Competitiveness, Projects Nº ENE2015-64914-C3-3-R and Madrid regional government (YEI fund), Grant Nº PEJD-2018-PRE/TIC-8571.

## CONCLUSION

- > With IRIO-OpenCL kernels, DAQ functionality is resolved so that the scientists can focus only on the processing algorithms.

- > FPGA development can be reduced by using OpenCL which works well with standardization software like NDSv3.

- > By combining these techniques, very demanding algorithms can be deployed to specialized hardware with the minimum effort.

**GRUPO DE INVESTIGACIÓN EN INSTRUMENTACIÓN Y ACÚSTICA APLICADA**