# Implementation of an FPGA-based DAQ and Processing system for Neutron-**Diagnostics using NDS, OpenCL and MTCA**

M. Astrain<sup>1</sup>, A. Carpeño<sup>1</sup>, S. Esquembri<sup>1</sup>, M. Ruiz<sup>1</sup>, J.Nieto<sup>1</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

Email: miguel.astrain@i2a2.upm.es

## **ID: 494**

# HIGHLIGHTS

•Neutron flux measurement is a good use case to test the implementation of hardware in FPGA using OpenCL-based tools. The algorithm is well-known, and benefits from high sampling rate devices.

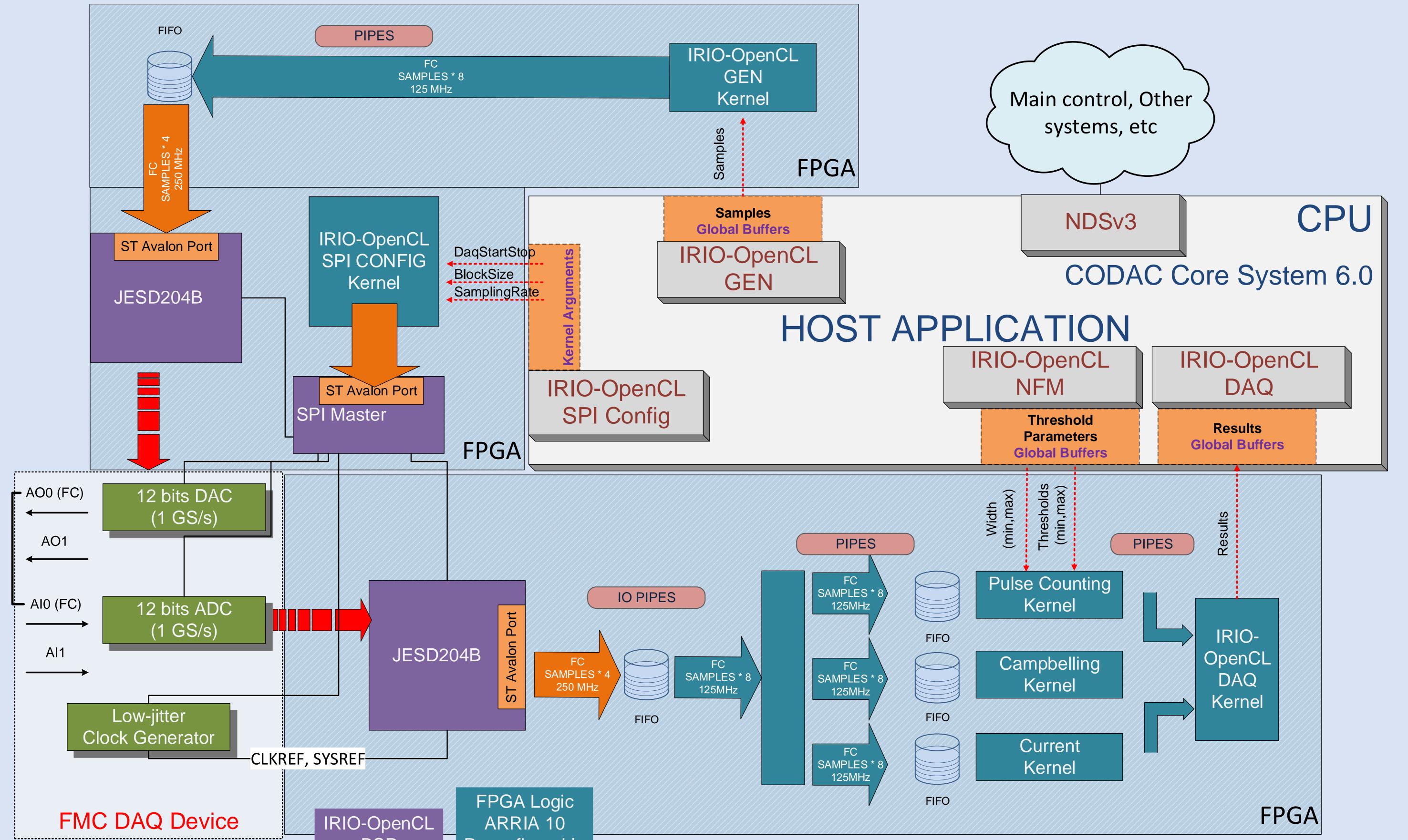

•A database of pulses is created, generating the waveforms either by a signal generator or using the DAC in the FMC module. The acquired signal by ADC in FMC module are processed in an IntelFPGA Arria10 FPGA.

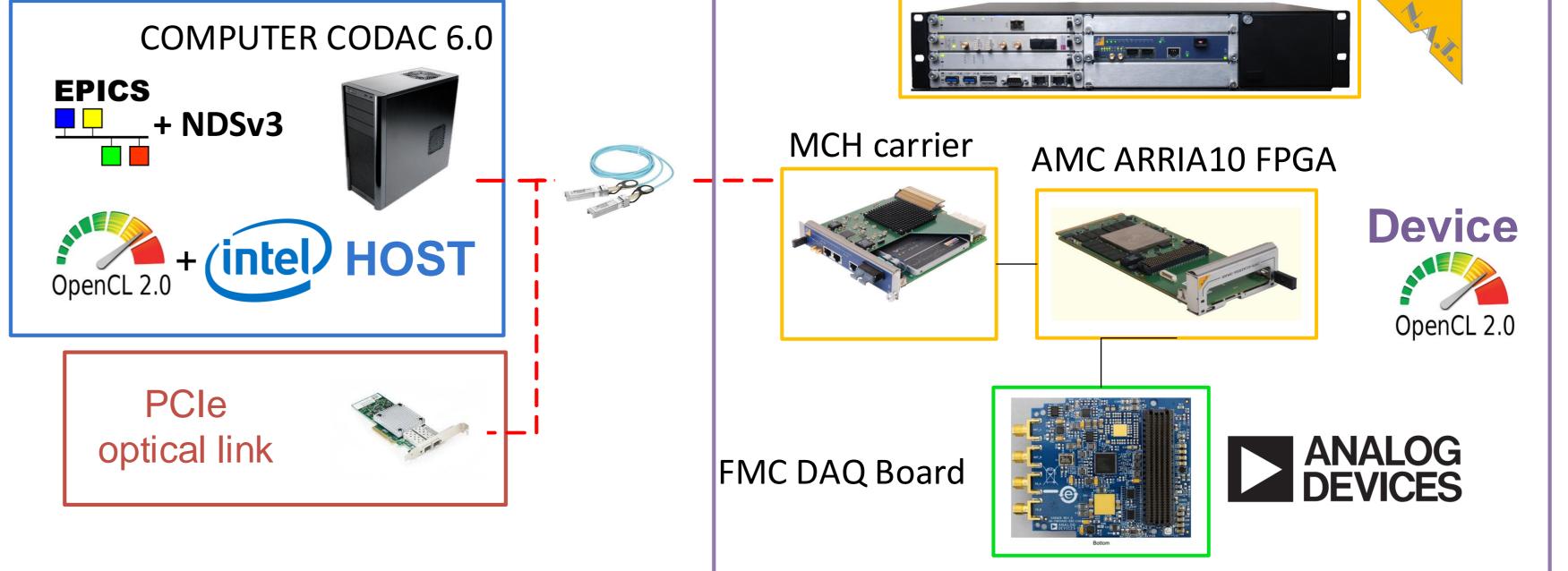

#### HARDWARE

MTCA chassis with a carrier hub, which provides an **optical PCIe interface**. The processing device is the N.A.T (AMC) module NAMC-Arria10-FMC board. This board consists of an **IntelFPGA ARRIA10** and includes an FMC (FPGA Mezzanine Card) connector where the **AD**-**DAQ2FMC-EBZ modu**le providing two **1GS/s ADC channels** together with two **1GS/s DAC** channels.

- •With the FPGA, the algorithm is divided into Kernels, which are synthesized to be executed in parallel.

- •The solution is implemented using MTCA.4 standard platform

## METHOD

The methodology to is described in contribution ID 490. Thursday session at 9.00! And poster in the afternoon!

### ACKNOWLEDGEMENTS

This work was supported in part by the Spanish Ministry of Economy and Competitiveness, Projects Nº ENE2015-64914-C3-3-R and Madrid regional government (YEI fund), Grant Nº PEJD-2018-PRE/TIC-8571.

#### CONCLUSION

- > The Intel OpenCL compiler generates an efficient pipeline to process data at very high throughput. HW is described using OpenCL language.

- > FPGA resource utilization with all the IRIO-OpenCL functionality is less than 50%.

- > The hardware is managed using NDSv3 allowing an easy connection to EPICS.

- > The complete platform is integrated in ITER CODAC Core System.