# The Implementation and operation of the 4<sup>th</sup> version of the KSTAR Fast Interlock System Myungkyu Kim, Taehyun Tak, Jaesic Hong National Fusion Research Institute mkkim@nfri.re.kr

## ABSTRACT

- 4th version of KSTAR Fast Interlock System (FIS) using NI c-RIO technology built and operated in 2018.

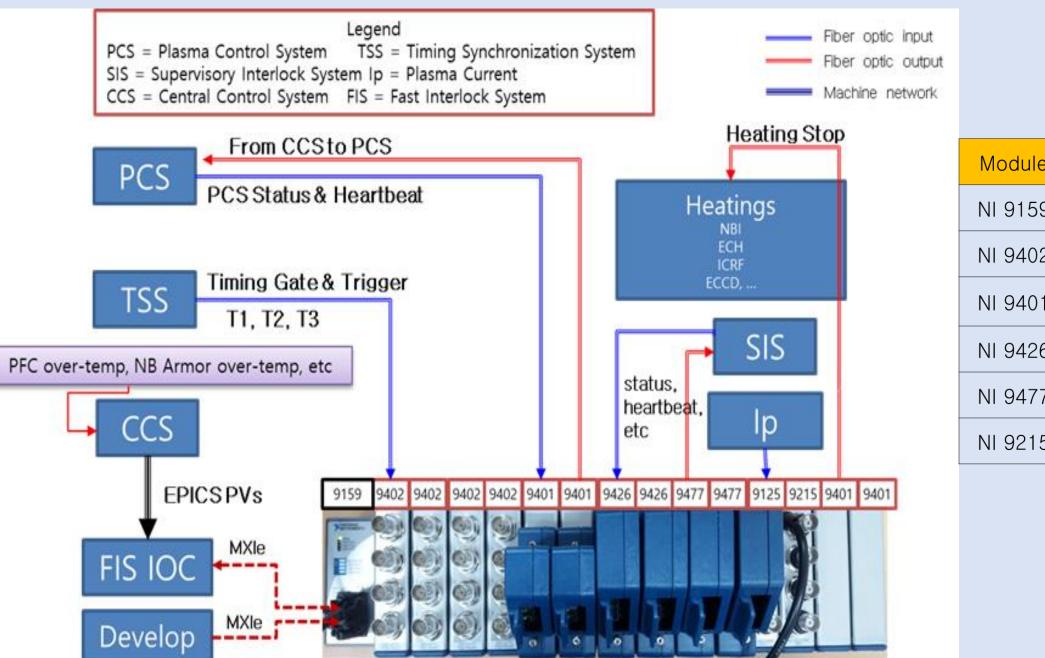

- The EPICS irio driver enables complete control and monitoring of the FPGA, and the distributed interlock information can be integrated in the FIS IOC via EPICS.

- The FPGA, which is responsible for signal processing at high speed, implements the event counter logic to record the event occurrence time.

# **OPERATION** and **RESULTs**

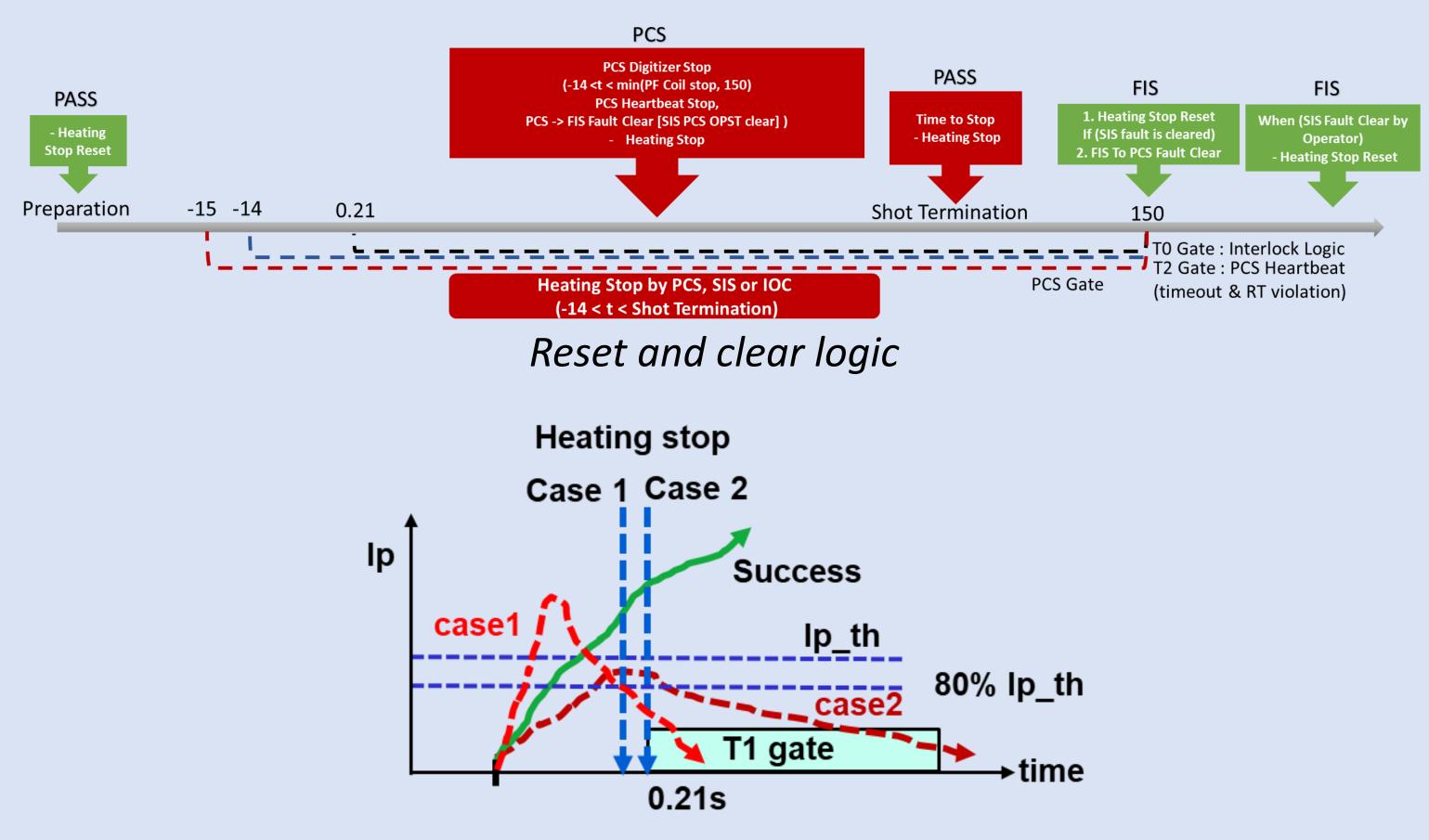

## **Reset and Clear faults**

Pulse Automation and Shot Scheduling(PASS), PCS, Timing interfaced FPGA logic.

**ID: 433**

Least operator's intervention.

#### **Performance Evaluation**

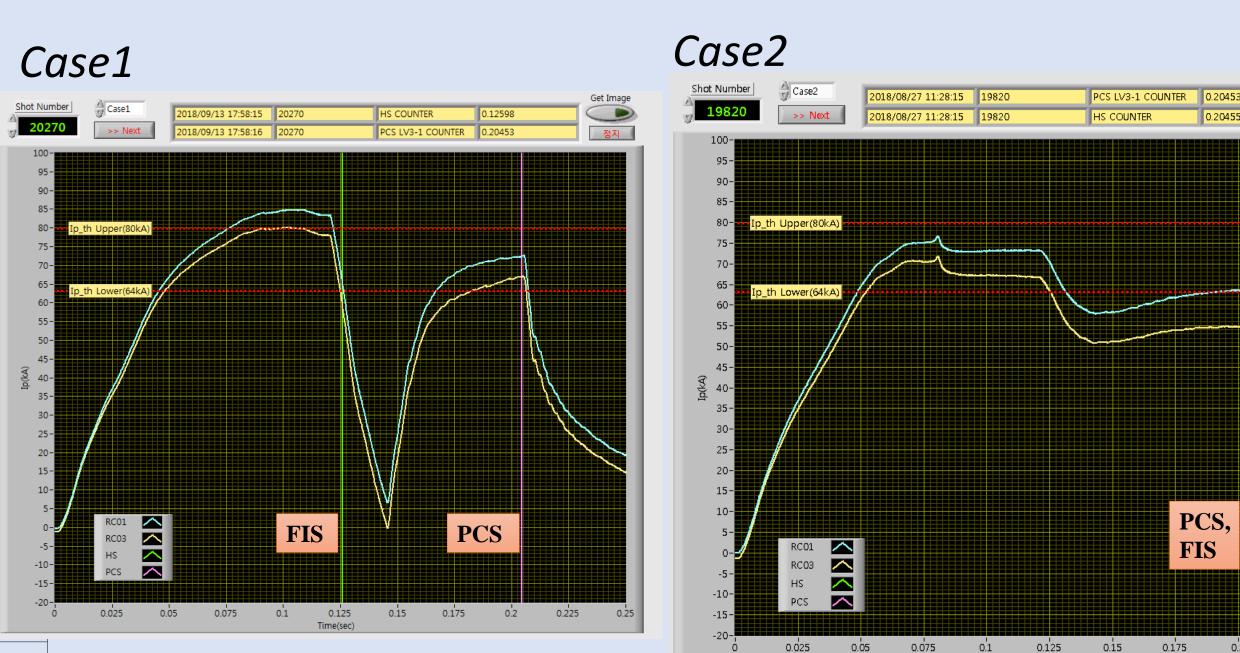

- Focus on start-up phase (<250ms)

- Analysis on Ip profile and Heating Stop(HS) time

- The event generated in the FPGA is displayed in 10 microseconds resolution by the 100 kHz operation period.

# INTRODUCTION

# History of KSTAR FIS [1], [2]

- 1<sup>st</sup> Version, 2009 : Central Control System +Plasma Control System using RFM within 200ms

- Version, 2012 : Fast interlock interface + TSS • 2<sup>nd</sup>

- 3<sup>rd</sup> Version, 2014 : 2nd Version + PFC, NB armor temp. faults

- 4<sup>th</sup> Version, 2018 : c-RIO+EPICS IOC

# **FIS protection logics [3]**

- Ip protection logic : FPGA processing

- PCS, SIS interface logic : information transfer using hardwire

- EPICS PV interface logic : information transfer using EPICS PV

# IMPLEMENTATION

## **FPGA** Programming

Labview FPGA module, EPICS irio driver [4] • 4 execution loops (Ip logic, Event count, heating stop, heart-beat check)

- Event counter value converted to Blip based discharge time.

- 100kHz Ip protection logic perfectly working and generated HS signal.

- Case1, case2 shows perfect working.

*Ip protection logic*

• Timing sync. With KSTAR TSS

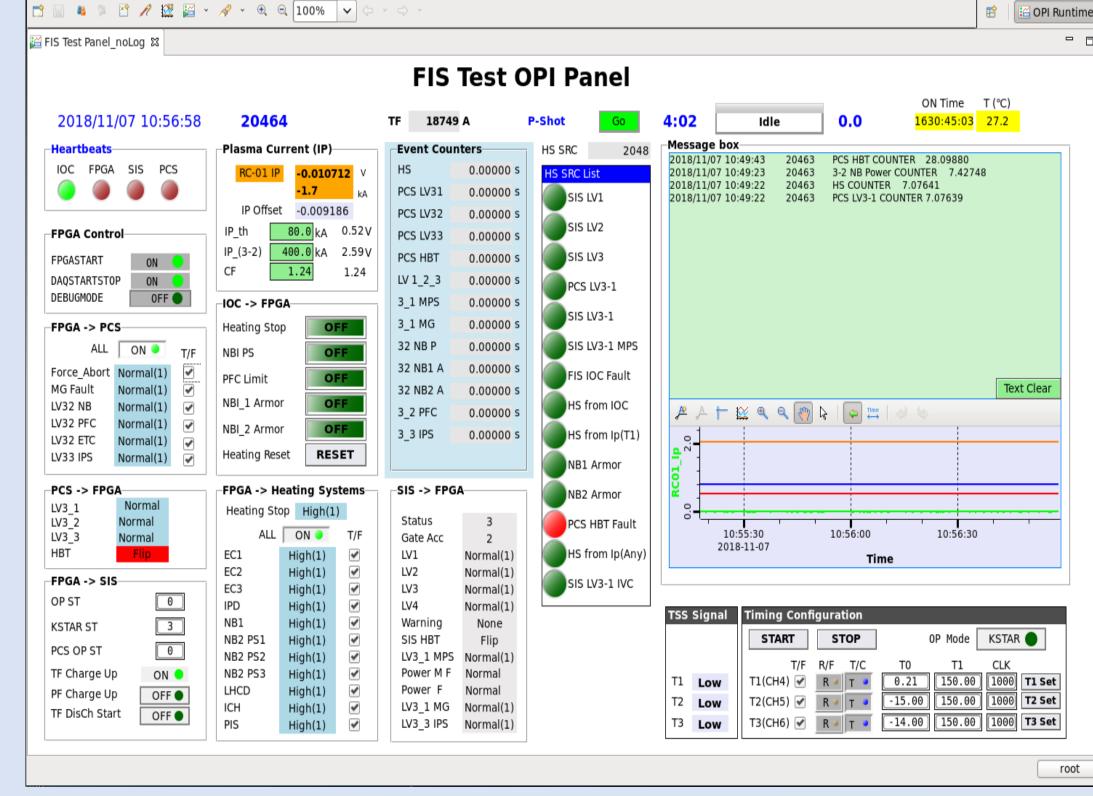

#### OPI

- Using EPICS Control System Studio(CSS)

- Linked with KSTAR shot based operation

| 2                                      | CS-Studio (on dev04-64bit) | _ <b>_</b> × |

|----------------------------------------|----------------------------|--------------|

| File Edit Search CS-Studio Window Help |                            |              |

|                                        |                            |              |

| Module  | Description                       | No. | Related Sys.     |     |

|---------|-----------------------------------|-----|------------------|-----|

| NI 9159 | 14-slot chassis, LX110 FPGA, MXle | 1   | FIS IOC          |     |

| NI 9402 | 4-ch, 55ns, DIO, BNC              | 4   | CTU              |     |

| NI 9401 | 8-ch, 100ns, DIO, 25pin D-SUB     | 4   | Heating sys. , f | °CS |

| NI 9426 | 32-ch, 7#s, DI, 37pin D-SUB       | 2   | SIS Input        |     |

| NI 9477 | 32-ch,8#s, DO, 37pin D-SUB        | 2   | SIS Output       |     |

| NI 9215 | 4-ch, 100kS/s/ch, 16 bit AI, BNC  | 2   | RC01             |     |

|         |                                   |     |                  |     |

#### C-RIO module datails

#### *Ip protection examples*

## CONCLUSION

• 4th version of KSTAR FIS worked without any problem during 2018 operation.

PCS,

FIS

0.225

0.175

0.15

Using FPGA event counter logic, FIS performance evaluation was done.

FIS OPI using CSS

- Event counter was very useful to specify the error/fault source.

- The level of Ip threshold should be reviewed and another protection logics can be added for the FIS upgrade.

# REFERENCES

- 1. M. Kim, et al., "The Implementation of KSTAR Fast Interlock System using c-RIO", ICALEPCS 2017

- 2. J. Hong, et al., "Development and operation of fast protection for KSTAR", Fusion Eng. Des. 112, 2016

- 3. T. Tak, et al., "Plasma protection mudule design for ITER CIS fast architecture", Fusion Eng. Des. 124, 2017

- 4. "IRIO EPICS device support-V1.2.0 user's manual", UPM, Spain